11:25 Texas Instruments. RFID считыватель транспондеров TIRIS | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

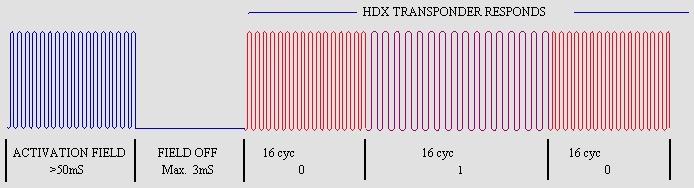

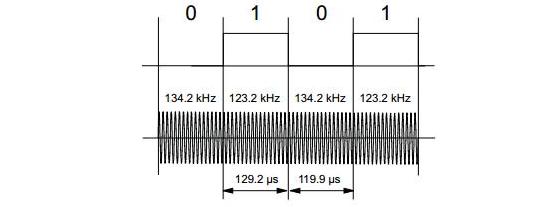

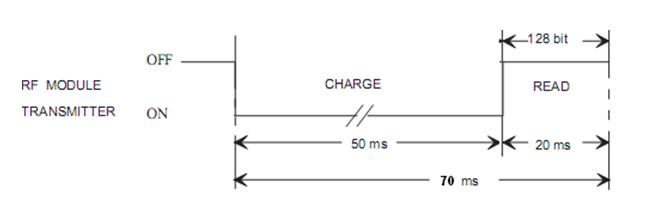

Для начала немного информации о том, какие стандарты и протоколы используются для обмена транспондерами TIRIS. Данные транспондеры работают в режиме HDX – транспондер имеет несколько циклов: цикл зарядки, активация, передача пакета, разрядка. Транспондер передает пакет только после того, как перестает работать генератор считывателя, который заряжает транспондер. Поэтому собственно и передача получается полудуплексная. Стандарт передачи имеет маркировку ISO 11784 & 11785 (HDX). Считыватель, сгенерировав цикл зарядки для транспондера порядка 50 мс, отключает генератор и ожидает передачи пакета транспондером (примерно 3 мс). Модуляция сигнала транспондера - FSK частоты 123.2КГц, 134.2 КГц. Частота, генерируемая считывателем для зарядки транспондера – 134.2Кгц. В моем случае транспондер маркировался как RI-TRP-WR2B. Существует множество форм-факторов для транспондеров TIRIS данного стандарта – брелки, карты, метки идентификации животных. Рассмотрим на картинке, как работает транспондер в режиме HDX. Видно, что после цикла зарядки 50 мс транспондер активируется и передает данные. Для передачи логического ‘0’ в пакете транспондер передает 16 циклов частоты 134.2КГц, для передачи логической ‘1’ передает 16 циклов частоты 123.2Кгц.

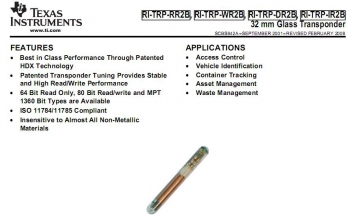

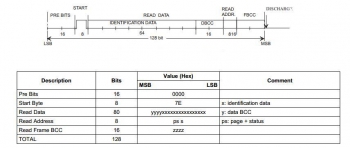

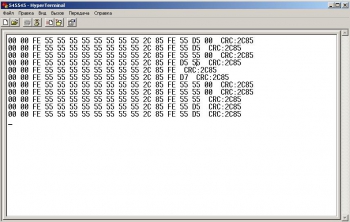

Ниже представлены данные транспондера, который был получен для экспериментов (образец RI-TRP-WR2B от Texas Instuments) На картинке видно как выглядит транспондер, описаны основные параметры изделия и область применения. Основные данные взяты из даташита TI. Для нас наиболее интересными параметрами будут временные диаграммы пакета транспондера и структура пакета. Получается, сам полезный пакет имеет длину 80 бит – 64 бита данных и 16 бит контрольной суммы CRC 16 CCITT. Пакет начинается с 16 битов заполненных ‘0’ заголовка, затем идет стартовый байт пакета 7E (для транспондеров Read Only, для перезаписываемых может быть FE стартовым), 64 бита пакета, 16 бит контрольной суммы. Далее могут идти дополнительные биты адресного пространства. В некоторых сериях транспондеров данного формата после битов пакета данных и контрольной суммы идет стоповый байт, который равняется стартовому байту. Стоповый (он же стартовый) байт может быть 7E или FE.

По временной диаграмме получается следующее. Весь цикл занимает около 70мс. Для считывания данных пакета транспондера (полный пакет) достаточно примерно 20 мс.

Логическая структура данных транспондера стандарта ISO 11784 & 11785. Таблица с данными взята из описания ISO 11784 & 11785. Взято из документации стандарта. Надеюсь, названия на английском параметров будут очевидны без перевода.

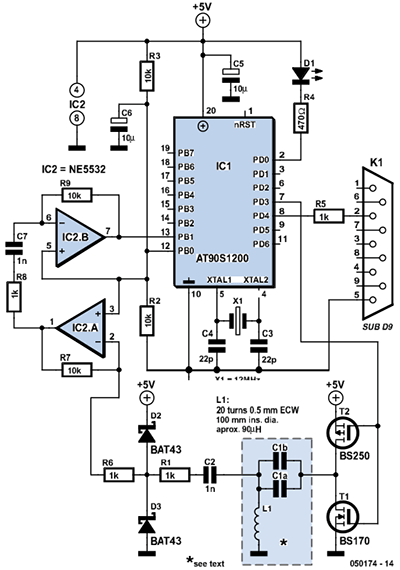

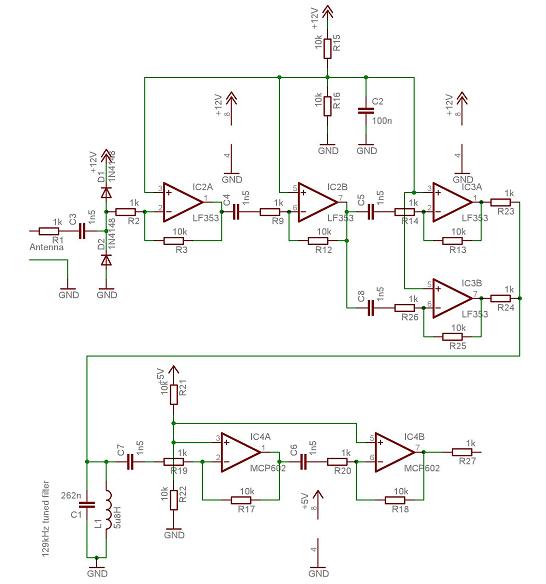

Принципиальная схема считывателя RFID транспондеров Tiris.

Первая версия схемы аналоговой части считывателя была построена на основе схемы опубликованной в журнале Elektor (2005-10) Ниже представлена оригинальная схема на основе статьи из данного журнала. Схема простейшая, особо подробные комментарии излишни при просмотре данной схемы. Используется усилитель на двух транзисторах mosfet (P и N канальный) для последовательного резонансного контура генератора. Можно сделать токовый усилитель на NPN и PNP транзисторах, но лучше конечно на MOSFET. Далее идет непосредственно сам контур. Контур настраивается на резонанс в середине диапазона принимаемых сигналов (129-130 Khz) поскольку у нас частоты сигналов 123.2КГц и 134.2 КГц. Далее стоят защитные диоды, поскольку пики колебаний могут достигать 100V. Затем стоят 2 каскада усиления на операционном усилителе NE5532 и выходной сигнал попадает на компаратор микроконтроллера. Для нормальной работы устройства потребуется настроить в резонанс контур генератора (катушка и конденсатор) иначе сигнал будет слишком слабый, будут большие потери по мощности, излучаемой генератором. В моем случае элементы побирались по прибору измерения LC достаточно точно, затем по осциллографу (по пикам амплитуды генератора) корректировалась катушка индуктивности для попадания в резонанс.

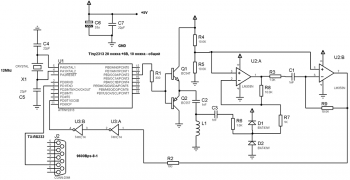

Поскольку в схеме используется контроллер АТ90S1200, давно снятый с производства было решено реализовать проект на контроллере АТTiny2313. На портале проектов журнала также есть ассемблерный код для АТ90S1200. Соответственно кому он интересен, может попробовать разбираться в данном коде и реализовать при желании на других контроллерах. Поскольку у меня такого желания не было разбираться с АТ90S1200 и ассемблерной реализацией решил сделать на языке С проект (CV Avr, WinAvr), кроме того решил изменить алгоритм работы устройства, отвязаться от аналогового компаратора и завести сигнал на вход тактирования внешним сигналом таймера. Таймер настраиваю на счет 16 импульсов сигнала и делаю прерывания для проверок частоты сигнала (по периоду прерываний). Во время прерывания проверяется состояние счетчика второго таймера, значение которого известно на основе основной частоты тактирования контроллера. Данный метод широко используется для измерения частоты и периода внешнего сигнала. Разумеется, для упрощения программы контроллера можно усовершенствовать схему, реализовать внешний делитель сигнала на счетчиках и получать уже по фронтам прерывания сигнал кратный периоду 16 импульсов. В следующих версиях схемы устройства данная идея будет реализовываться. Это позволит собрать устройство даже на контроллере типа Tiny13. Ниже представлена первая версия считывателя Tiris транспондеров. Генератор и приемник сигнала в данном случае размещены в одной схеме. Схема практически повторяет оригинальную схему от Elektor. За отсутствием под рукой мосфетов собиралось из того, что было под рукой. Детали самые распространенные и дешевые. Каскад усилителя сделан на NPN транзисторе bc547 и PNP транзисторе bc557. Операционный усилитель поставлен LM358N. По-хорошему нужно ставить что-то лучше, типа быстродействующего rail-to-rail (размах выходного сигнала до напряжения питания) операционного усилителя. На выходе каскада стоит пара буферных элементов (инверторов Шмитта) с гистерезисом для лучшей крутизны фронтов. Выход данных транспондера (приемная часть) подключен на вход 9 (T1) контроллера. Это вход внешнего источника тактового сигнала Timer1. Вход генератора подключается к 14 ножке. Импульсы для активации транспондера 132.2 Кгц генерируются в течение времени порядка 50ms, затем генератор отключается и таймер переключается в счетный режим. Данные считывателя передаются на ПК посредством интерфейса RS232. Поскольку уровни контроллера TTL для передачи на порт ПК потребуется поставить преобразователь TTL-RS232. На схеме указан разъем D-SUB9, в реальности предполагается подключение преобразователя TTL-RS232 для подключения к порту ПК. Простейший преобразователь TTL-RS232 можно сделать на 1 транзисторе. Схема собиралась на макете, выход подключался к плате готового преобразователя COM-USB на чипе TUSB3410, который имеет вход TTL. Собственно поэтому преобразователя TTL-RS232 не потребовалось в моем случае. Во второй версии устройства используется отдельно приемная часть. Для передающей части оставляем только усилитель на 2-х транзисторах и резонансный последовательный LC контур. Все остальное переносится в часть приемника сигнала с отдельной антенной. Это удобно при компоновке в виде двух модулей с рамочными антеннами, между которыми считываются данные транспондера. На входе схемы стоят защитные диоды. Схема имеет 2 каскада усиления на операционных усилителях LF353 и MCP602. MCP602 как раз и есть rail –to-rail операционный усилитель (с амплитудой выхода равной амплитуде напряжения питания при однополярном питании) о чем было сказано ранее по замечаниям предыдущей схемы. Общее усиление схемы порядка 1000. Между каскадами установлен фильтр, который настраивается на 129-130Кгц (середина диапазона). Полоса пропускания фильтра будет порядка 20Кгц что с запасом покрывает наш диапазон. Оконечные усилители первого каскада установлены в параллель, поскольку используется пассивный параллельный LC фильтр после каскада. Выход схемы приемника подключаем к ножке тактирования таймера внешним сигналом T1 (9 ножка). Как можно видеть на схеме предусмотрена развязка между каскадами по постоянному току - установлен разделительный конденсатор. Индикатор чтения транспондера (светодиод) подключается к ножке PORTD.0 (2 ножка) контроллера (на схеме не указан). Включение светодиода аналогично оригинальной схеме из журнала Elector (анодом к +5 питания через сопротивление 330-470 Ом).

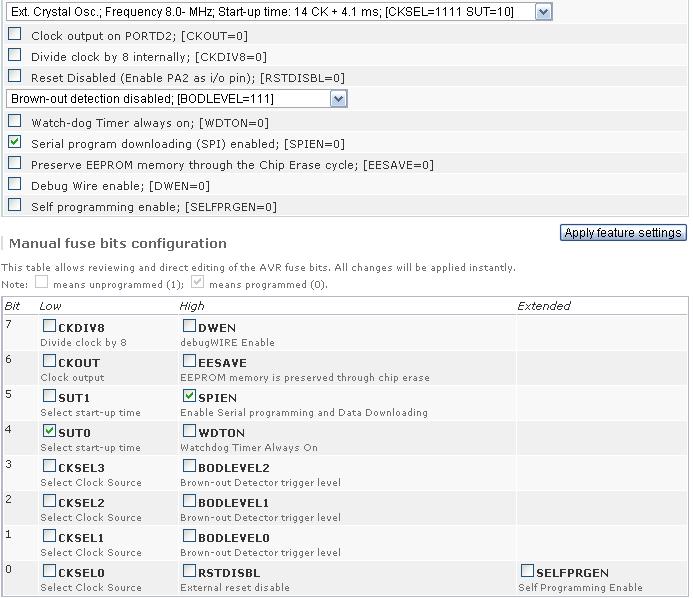

Версия 2 устройства приемной части. Отдельно используется приемник сигнала транспондера. Проект собирался на макетной плате, поэтому печатной платы на данный момент нет. Выход схемы подключался посредством преобразователя на TUSB3410 к USB порту ноутбука. Для подключения к RS232 порту стационарного ПК ставится преобразователь TTL-COM на выход 3 (TX) контроллера. Данные приема пакетов тестировались через стандартную утилиту HyperTerminal. Данные подключения COM порта : скорость 9600bps, 8 бит пакет, 1 бит четности, без управления потоком. Данные в пакете далее контрольной суммы никак не проверяются в программе. Для корректной проверки пакета достаточно приема заготовка, тела пакета и CRC. Ограничение по приему данных пакета установлено 128 бит. Пакет транспондера при наличии информации читается до данного ограничения. Такой алгоритм установлен, поскольку длина пакета разных моделей транспондеров Tiris может отличаться. В нашем случае считаем, что данные прочитаны корректно, если получили пакет основных данных и проверили его CRC. Немного информации по прошивке контроллера. Фьюзы устанавливаются для работы от кварцевого резонатора 12МГц. Поскольку в контроллере Tiny2313 по умолчанию установлен фьюз делителя частоты на 8, его потребуется убрать. Хороший ресурс для расчета настроек контроллера http://www.engbedded.com/fusecalc. Например, в данном случае устанавливаем настройки таким образом.

К статье прилагается архив с проектом на CVAvr. С транспондерами TRP-WR2B дальность считывания получилась в образце порядка 10-15см (зависит от положения транспондера). Разумеется, можно существенно умощнить усилитель (в первую очередь) для генератора и переработать приемную часть, чтобы получить расстояние больше данных значений. Кроме того расстояние будет зависеть от настройки контура генератора в резонанс. Прикрепленные файлы:

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Всего комментариев: 0 | |